本文共 5200 字,大约阅读时间需要 17 分钟。

本节书摘来自异步社区《Cadence 16.6电路设计与仿真从入门到精通》一书中的第1章,第1.1节,作者: 王超 , 胡仁喜等 更多章节内容可以访问云栖社区“异步社区”公众号查看。

第1章 Cadence概述

Cadence 16.6电路设计与仿真从入门到精通

内容指南Cadence为挑战简短、复杂、高速芯片封装设计,推出了以Windows XP的操作平台为主的Cadence SPB 16.6。

本章将从Cadence的功能特点及发展历史讲起,介绍Cadence SPB 16.6的安装、界面、使用环境,以使读者能对该软件有一个大致的了解。

知识重点

- Cadence简介

- Cadence软件的安装

- Cadence SPB 16.6的启动

1.1 Cadence简介 方块

Cadence公司在EDA领域处于国际领先地位,旗下PCB设计领域有市面上众所周知的OrCAD和Allegro SPB两个品牌,其中OrCAD为20世纪90年代的收购品牌。Allegro SPB为Cadence公司自有品牌,早期版本称为Allegro PSD。经过10余年的整合,目前Cadence PCB领域仍执行双品牌战略,OrCAD覆盖中低端市场(以极低的价格就可以获得好用的工具,主要与Protel和Pads竞争),Allegro SPB覆盖中高端市场(与Mentor和Zuken竞争)。

(1)OrCAD涵盖原理图工具OrCAD Capture、Capture CIS(含有元件库管理之功能),原理图仿真工具PSpice(PSpiceAD、PSpiceAA),PCB Layout工具OrCAD PCB Editor(Allegro L版本,OrCAD原来自有的OrCAD Layout在2008年已经全球范围停止销售),信号完整性分析工具OrCAD Signal Explorer(Allegro SI基础版本)。

(2)Allegro SPB涵盖原理图工具Design Entry CIS(与OrCAD Capture CIS完全相同)、Design Entry HDL(Cadence旧Concept HDL),原理图仿真工具Allegro AMS Simulator(即PSpiceAD、PSpiceAA),PCB Layout工具 Allegro PCB Editor(有L、Performance、XL、GXL版本),信号完整性分析工具Allegro PCB SI(有L、Performance、XL、GXL版本)。

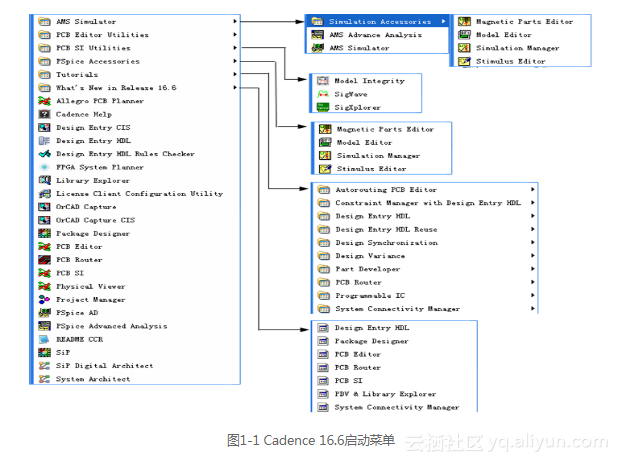

(3)Cadence 16.6与之前的几个版本在功能模块上既有相同的地方,也有不同之处,下面对比图1-1所示的启动菜单简单介绍一下具体功能模块。

- Design Entry CIS:Cadence公司收购的OrCAD公司的旧版本Capture和Capture CIS,是国际上通用的、标准的原理图输入工具,设计快捷方便,图形美观,与Allegro软件平台实现了无缝链接。

- Design Entry HDL:是旧版本的Concept HDL,提供了基于Design Capture环境的原理图设计,允许使用表格、原理图和Verilog HDL进行设计。

- Design Entry HDL Rule Checker:检查Design Entry HDL规则的工具。

- Library Explorer:包括Part Developer和Library Explorer两个功能,进行数字设计库的管理,可以调用建立Part Developer、PartTable Editor、Design Entry、Packager-XL和Allegro的元件符号和模型的工具。

- OrCAD Capture:原理图设计工具。

- OrCAD Capture CIS:原理图设计工具。

- Package Designer:高密度IC封装设计和分析。

- PCB Editor:完整的PCB设计工具。

- PCB Router:CCT布线器。

- PCB SI:建立数字PCB系统和集成电路封装设计的集成高速设计和分析环境,可以解决电器性能相关问题,如信号完整形、串扰、电源完整性和EMI。

- Physical Viewer:Allegro浏览器模块。

- Project Manager:Design Entry HDL的项目管理器。

- PSpiceAD:原理图仿真工具。

- Sip:是一种在基板上同时粘着两块以上芯片的单片封装。

- System Digital Architect:Sip数字结构图。

- System Architect:系统结构图。

1.1.1 Cadence特点

Cadence设计系统公司宣布其Allegro 16.6 Package Designer与系统级封装(SiP)布局解决方案支持低端IC封装要求,满足新一代智能手机、平板电脑、超薄笔记本电脑的需要。Allegro 16.6 Package Designer与Cadence SiP Layout的新功能包括芯片置入腔体功能,即一种能提高效率的全新键合线应用模式,以及一种晶圆级芯片封装(WLCSP)功能,为IC封装设计提供业界最全面的设计与分析解决方案。Cadence已经有能力通过Allegro工具,来解决与小型轻薄型消费电子产品IC封装有关的挑战。全新直观的键合线应用模式可通过专注于特定的焊线工艺提升产能。Cadence Allegro套件可实现高效率的WLCSP流程,可读写更简练的GDSII数据。全新的高级封装布线器基于Sigrity™技术,可大大加快封装底层互联的实现。封装评估、模型提取、信号与功率完整性分析,也是基于Sigrity™技术,并都已经被集成到Allegro 16.6解决方案中。这使得IC封装设计中需要确认及签署的分析结果更加容易快捷。

Cadence Allegro的全新改良可实现具有更高可预测性和有效率的设计周期。此外,Allegro协同设计流程的改良可增强合作,芯片与PCB设计团队都能提高系统级的表现,降低总体系统成本。

与Protel提供的一个完整的设计工具包不同,Cadence Allegro工具提供了极其灵活的配置,通过拆分成许多功能模块,以满足不同需求的客户找到最贴切的方案,从而大幅节省成本。相比Allegro 16.6之前的Pspice只能支持单核,而新的Pspice可支持多核(超过4核),因而在仿真速度方面最高提升4倍。加强了与用户互动的功能,可通过云存储将设计放到云端。此外,在Team Design、小型化、三维接口等方面都有很好的改进。

Allegro 16.6 能够将高速界面的时序闭合加快30%~50%,这有赖于时序敏感型物理实现与验证,是其对应的业界首个电子 CAD(ECAD)团队协作环境,面向使用Microsoft SharePoint技术的PCB设计。

Allegro 16.6 产品线的新功能有助于嵌入式双面及垂直部件的小型化改良,改进时序敏感型物理实现与验证,加快时序闭合,并改进ECAD和机械化MCAD协同设计,这些都对加快多功能电子产品的开发至关重要。Allegro套件的PCB设计小型化功能在16.5中已经提供,Allegro 16.6产品套件继续利用嵌入式有源及无源元件最新的生产工艺,解决电路板尺寸不断缩小有关的特定设计问题。元件可利用z轴垂直潜入到PCB内层,大大减少x和y轴布线空间。

Allegro 16.6通过自动交互延迟调整(AiDT)加快时序敏感型物理实现。自动交互延迟调整可缩短时间,满足高级标准界面的时序约束,例如DDR3等,缩短的程度可达30%~50%。AiDT可帮助用户逐个界面地迅速调整关键高速信号的时间,或将其应用于字节通道级,将PCB上的线路调整时间从数日缩短到几个小时。EMA Timing Designer结合Allegro PCB SI功能,帮助用户迅速实现关键高速信号的时序闭合。

1.1.2 Cadence新功能

1.Cadence 推出最新版本中原理图部分OrCAD Capture V16.6,新增功能如下。(1)在SigXplorer设定的拓朴结构及 Constraints 可直接回编到电路图上,大幅简化与缩短Pre-Sim的作业流程。

(2)自定义菜单和工具栏:自定义 Menu和Toolbars,如改变Menu item位置和名称等。其中,文件位置在“shareorResources”路径下。

(3)修改XML文件,未保存页面会标示“”:修改过的Design or Page or Library会在未保存前,标示Mark()星号。

(4)增强了查找功能。

- 可指定找寻某一个属性的值,如pcb footprint=PLCC28Note:属性名称需为完整字串,万用字元(*)只支援参数值字串。

- 搜寻区间范围的零件,如U4[1-4]Note:当两个功能都被开启时,常规描述搜寻只支援属性值的字串。

- 一次性替换相同网络名称的页间连接符,将A名称换成B名称。

(5)增强 Cache 的更新:可在设计 Cache中一次选取多个零件,透过替换Cache 换成同一个零件。

(6)设置用户给定标志。

当Reference清成“?”时,同类型复合式零件可保留Section。

可以保留用户自订的参照。注意保留部件参照可通过以下几个步骤。Edit Property

直接修改Part Reference Value。

从PCB Board 修改完后Back Annotate 回线路图,Preserve Designator(保留原本的Section),Preserve User Assigned Valid References(修改过的Reference会加上“_”底线)。

(7)在阶层式电路中摆放零件时,可依照整份Project自动编号,避免零件编号重复。(8)可直接View旧版本的线路图,当执行存档动作时,才会跳出警示讯息是否要Update Design。

(9)利用菜单或是在分页上,选择一次关闭所有开启的Page或是关闭所有Page但保留当前view的这一页。

(10)透过TCL/TK编写DRC检查。

(11)对于Project的Save as除了OPJ档外,也能把DSN或是Output File一并存入指定的资料夹中。

(12)在 BUS 线上,直接放上 NetGroup名称。

(13)可针对Unname NetGroup里的成员调整顺序。

(14)直接从 NetGroup 中选择要接的NetGroup及不想接的。

(15)现在不论Port或是Offpage都可清楚辨识属于哪一个NetGroup。

(16)利用Find功能寻找NetGroup Pin。

2.Cadence推出最新版本中电路板设计部分Allegro16.6,新增功能如下。

(1)当PCB Layout工程师在网络表传输完成后,这些Constraint设定也会随著网络表格的导入而自动带到Allegro、OrCAD PCB Layout的Constraint Manager环境中。

(2)当电路图被再次利用时,读者无须再去重复先前的作业,所有的拓朴结构、T点、Xnet及Constraint资料都已保存在电路图上。

3.Cadence推出最新版本中仿真分析部分PSpice16.6,新增功能如下。

(1)使用操作改进与提升:

软件本身提供Leaning PSpice学习教程、快速调用PSpice元器件、PSpice模型加密支持256-bit AES加密算法和新增PSpice仿真元件库。

- 支持IBIS模型到PSpice模型导入。

- 新增What-if设计流程。

- Model Editor支持隐藏引脚原理图符号导入。

(2)核心功能改进与提升:仿真精度提高,支持64位数据精度、仿真收敛性大大增强,提供了众多可供用户选择的设置、仿真速度提升,支持多核运算、I/O优化,增强PSpice处理大数据量波形文件能力。

(3)Tcl的支持与集成。

4.Cadence 推出最新版本中编程部分FSP16.6,新增功能如下。

(1)直接调用已有的PCB设计文件,利用FSP来重新设计或重复使用PCB文件中FPGA部分。

(2)新增滤波,匹配电路需要的电阻,电容等。

(3)可以整体添加设计中所有电源管脚的退耦电容。

(4)在PCB电路板设计Allegro下面也可以自动换管脚。

(5)调入 FSP 数据后新增各种自动换管脚形式,使FPGA设计变得更加高效简单。

(6)新增文档对比功能,用户可以根据文档比较来确认管脚交换前后的改动。

转载地址:http://ykhbx.baihongyu.com/